Implementation of Slanted Sidewall Gates Technology in the Fabrication of S-, X-, and Ka-band AlGaN/GaN HEMTs

K.Y. Osipov, S.A. Chevtchenko, O. Bengtsson, P. Kurpas, F. Brunner, N. Kemf, and J. Würfl

Published in:

Int. Conf. on Compound Semiconductor Manufacturing Technology (CS ManTech 2014), Denver, USA, May 19-22, pp. 189-192 (2014).

Abstract:

Currently the so-called "embedded gate process" where the gate is processed into an insulator trench is commonly used for AlGaN/GaN HEMT gate fabrication. In this work we present a new approach for fabricating slanted sidewall embedded gates with dimensions of 500 nm, 250 nm and 100 nm. In order to perform evaluation of a new technology, standard vertical gate approach was used for fabrication of reference transistors with gate lengths of 500 nm and 250 nm. Both technologies were used for fabrication of transistors using different heterostructures appropriate for the respective gate length. For slanted gate formation thermally reflowed ZEP520A e-beam resist has been applied in conjunction with anisotropic ICP etching of a SiNx layer. DC and large-signal RF characteristics as well as transistor yield on 4 inch SiC wafers were similar for both technologies. DIVA measurements of devices with gate length 500 nm showed significantly different drain current collapse for slanted and vertical gate transistors fabricated on wafers from different vendors. A possible explanation of this difference is given.

Ferdinand-Braun-Institut, Leibniz-Institut für Höchstfrequenztechnik, Gustav-Kirchhoff-Straße 4, 12489 Berlin, Germany

Keywords:

Ka-band, GaN HEMT, embedded gate technology, ZEP 520A

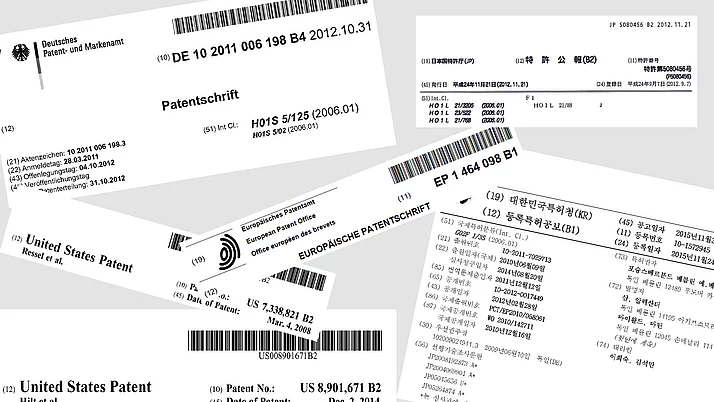

Copyright 2014 CSManTech All Rights Reserved. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from CSManTech.

Full version in pdf-format.