Vergleich von GaN-auf-Si Wafern für 600 V Schalttransistoren

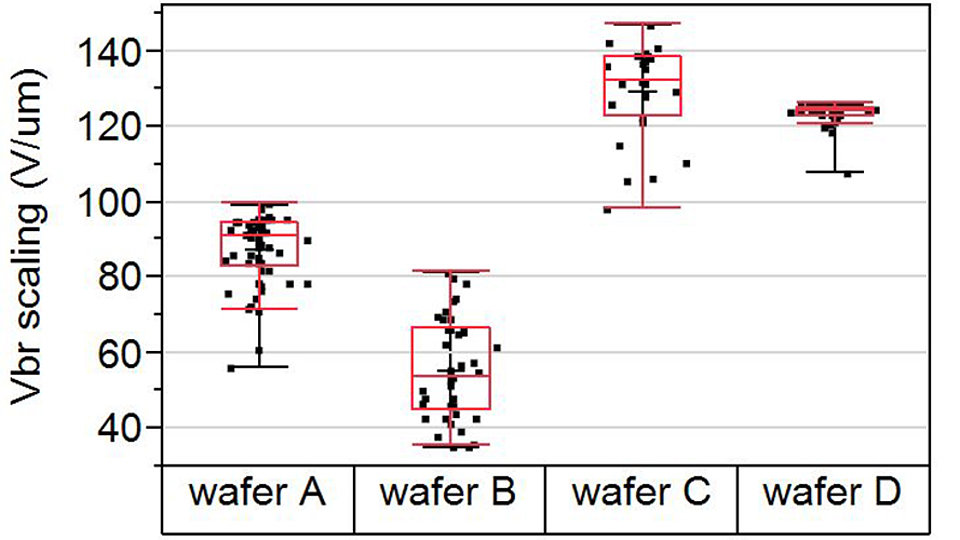

Abb. 2: Skalierung der Durchbruchspannung in V pro µm Gate-Drain-Abstand für vier unterschiedliche GaN-auf-Si Wafer.

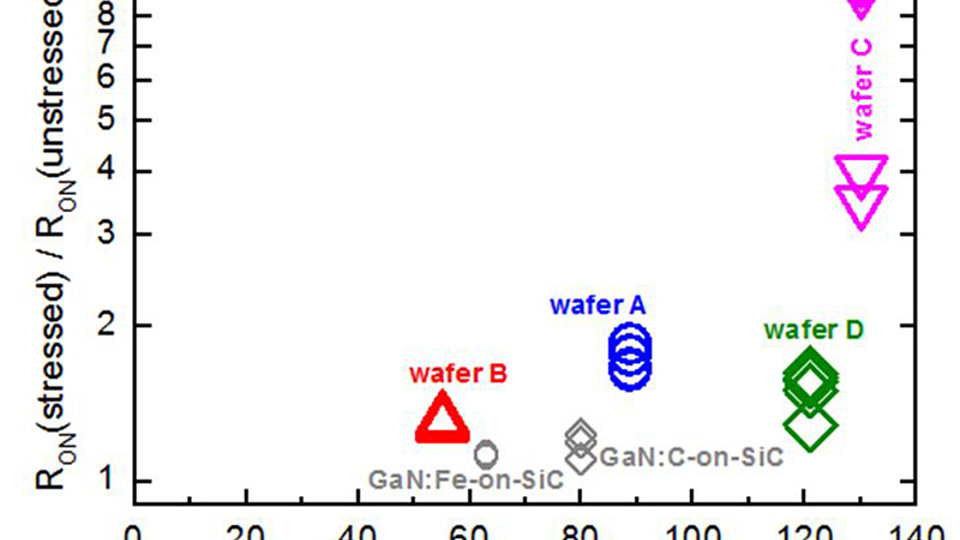

Abb. 3: Zunahme des dynamischen Einschaltwiderstands in Abhängigkeit der lateralen Durchbruchsspannungskalierung für die Wafer A bis D. RON wurde 0.2 µs nach dem Einschalten des bei 65 V gesperrten Transistors bestimmt. Resultate für zwei im FBH gewachsene GaN-auf-SiC Wafer (in grau) sind ebenfalls dargestellt.

Zur Herstellung von GaN-basierten selbstsperrenden 600 V / 70 mΩ Schalttransistoren für leistungselektronische Anwendungen setzt das FBH standardisierte Prozessmodule ein. Dabei wurden in einer Studie unterschiedliche kommerzielle 4“ GaN-auf-Si Wafer (Abb. 1) aus Japan und Europa verwendet. Wegen der niedrigen Substratkosten und der großen verfügbaren Waferdurchmesser ermöglichen derartige Wafer die kostengünstige Herstellung von GaN-Transistoren. Außerdem können vorhandene Prozesslinien aus der Si-Technologie eingesetzt werden.

GaN-auf-Si Epitaxie für 600 V AlGaN/GaN HFETs ist eine große Herausforderung. Im Vergleich zu anderen Substraten (z.B. Saphir oder SiC) hat Silizium eine schlechtere Anpassung der Gitterkonstanten und des Wärmeausdehnungskoeffizienten an GaN, was zu Waferverbiegung führt und die GaN-Schichtdicke auf etwa 5-6 µm begrenzt. Aber wegen des leitfähigen Si-Substrats werden für eine ausreichende elektrische Isolation besonders dicke GaN-Pufferschichten benötigt. Die nötige Spannungsfestigkeit kann dann nur noch durch den Einbau tiefer Störstellung mittels Kohlenstoffdotierung erreicht werden. Jedoch laden sich diese tiefen Störstellung bei den hohen Transistorsperrspannungen auf und führen nach dem Einschalten des Transistors zu einem verarmten Transistorkanal. Dieses Dispersionsphänomen wird oft als erhöhter dynamischer Einschaltwiderstand (RON) bezeichnet. Das Dotierprofil und noch andere Wachstumsparameter müssen daher für eine hoher Spannungsfestigkeit einerseits und gute dynamische Eigenschaften andererseits gut ausbalanciert werden. Der dabei gewählte Arbeitspunkt wurde für 4 Wafer unterschiedlicher Hersteller analysiert.

Die Wafer zeigen generell eine hohe laterale Spannungsfestigkeit von VBR > 50 V/µm, dennoch streut diese für die unterschiedlichen Wafer A bis D um mehr als das Doppelte (Abb. 2). Dabei ist die laterale Spannungsfestigkeit als Durchbruchspannung pro Gate-Drain-Abstand definiert. Die eingesetzte Kohlenstoffdotierung zur Erzielung der hohen Spannungsfestigkeiten führt dabei zu unterschiedlich starken Dispersionseffekten im Transistorschaltbetrieb (Abb. 3). Wafer C weist 130 V/µm Spannungsfestigkeit auf aber die Erhöhung des dynamischen RON (> x3) wird keinen effizienten Schaltbetrieb der Transistoren ermöglichen. Dem entgegengesetzt hat Wafer B die geringste Erhöhung des dynamischen RON (~x1.3) aber auch die geringste Spannungsfestigkeit ( 52 V/µm). Wafer D weist mit moderater Dispersion und hoher Spannungsfestigkeit wohl den geeignetsten Kompromiss auf.

Der Zielkonflikt zwischen VBr und dynamischen RON wir im Vergleich von Wafer A und Wafer B offensichtlich. Beide Wafer weisen einen ähnlichen epitaktischen Aufbau auf, unterscheiden sich aber in der Tiefe ab der der kohlenstoffdotierte GaN-Puffer unterhalb des 2DEG-Kanals einsetzt; 100 nm für Wafer A und 500 nm für Wafer B. Der dünnere undotiete GaN-Kanal des Wafers A liefert ein höheres VBr aber auch eine höhere Dispersion, da sich die geladenen Störstellen näher an dem Elektronenkanal befinden.

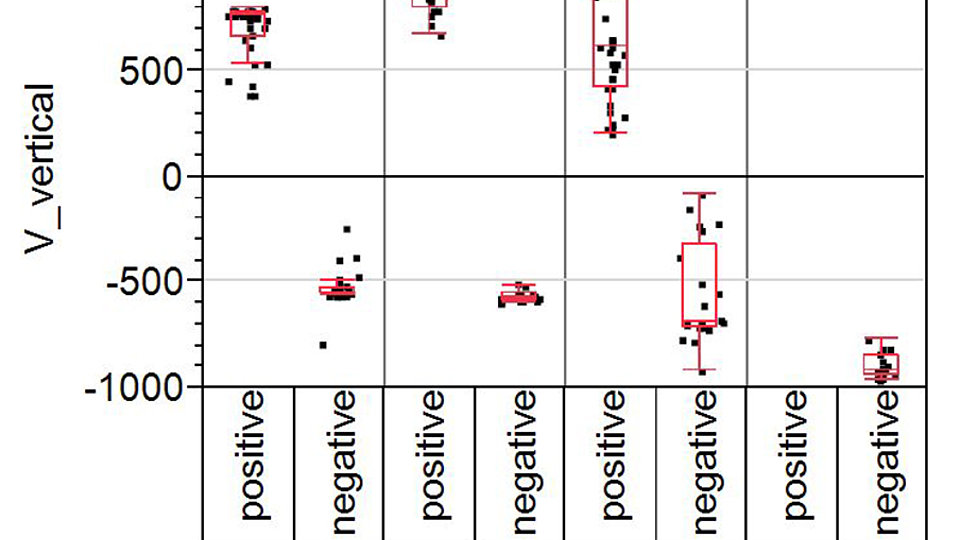

Transistorparameterstreuung innerhalb der Wafer erwies sich als weiteres Problem, wie die Verteilung der vertikalen Durchbruchspannung (Abb. 4) zeigt. +600 V vertikale Spannungsfestigkeit werden für den Transistorbetrieb mit Source-verbundenem Substrat benötigt. Aber viele Teststrukturen auf den Wafern A und C erreichen nicht diese Spannung, obwohl der jeweilige Wafermedian oberhalb +600 V liegt.

Publikationen

O. Hilt, E. Bahat-Treidel, A. Knauer, F. Brunner, R. Zhytnytska, and J. Würfl, "High-voltage normally OFF GaN power transistors on SiC and Si substrates", MRS Bull., vol. 40, no. 05, pp. 418-424 (2015).

O. Hilt, R. Zhytnytska, J. Böcker, E. Bahat-Treidel, F. Brunner, A. Knauer, S. Dieckerhoff and J. Würfl, "70 mΩ / 600 V Normally-off GaN Transistors on SiC and Si Substrates" Proc. 27th International Symposium on Power Semiconductor Devices & IC's (ISPSD 2015), May 10-14, Hong Kong, China, pp. 237-240 (2015).