Selbstsperrende 75 mOhm / 600 V GaN-Schalttransistoren auf SiC- und Si-Substraten

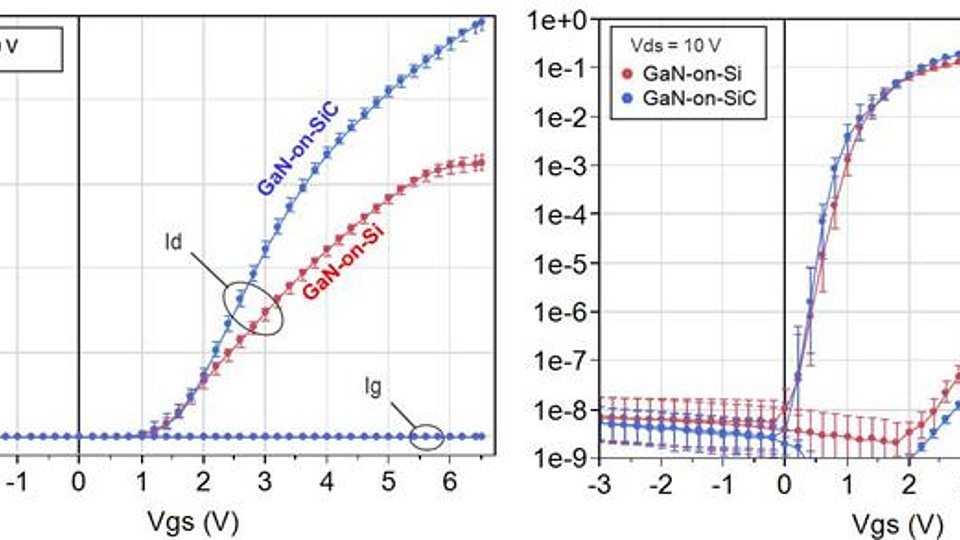

Abb. 2: Eingangskennlinie (Waferverteilung, Median, Percentilen) für GaN-auf-Si- und GaN-auf-SiC-Transistoren mit 3,2 mm Gateweite – lineare (l.) und logarithmische (r.) Darstellung

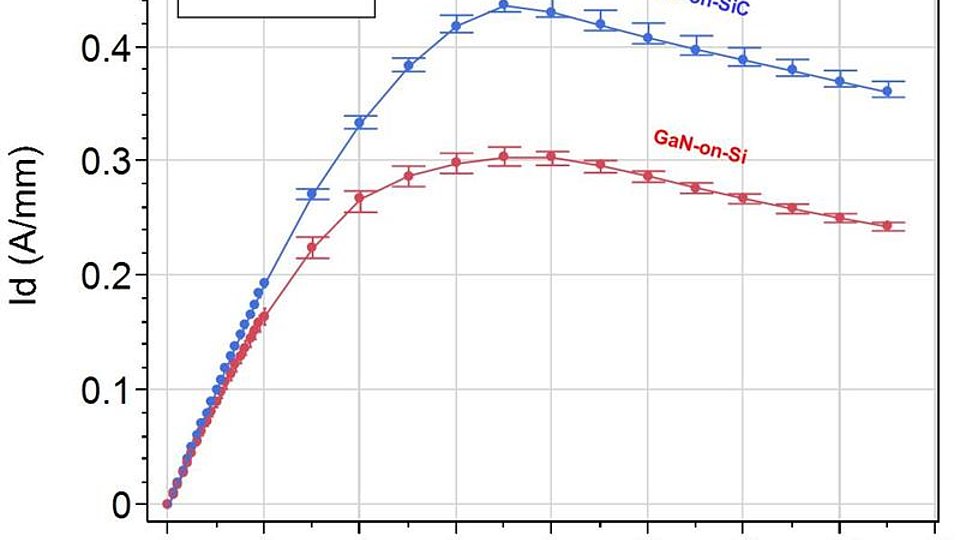

Abb. 3: Ausgangskennlinie (Waferverteilung, Median, Percentilen) für eingeschaltete GaN-auf-Si-und GaN-auf-SiC-Transistoren mit 3,2 mm Gateweite

GaN-basierte Leistungstransistoren für hohe Spannungen ermöglichen dank ihres geringen flächenspezifischen Einschaltwiderstands und der geringen Schaltverluste effiziente Leistungskonverter mit besonders hoher Leistungsdichte. FBH-Transistoren mit auf SiC-Substraten gewachsenen GaN-Schichten unterbieten dabei Si-basierte Super-Junction-MOSFETs in Bezug auf ihre niedrige Schaltenergie (Eoss = 5 µJ bei 400 V für RON = 65 mΩ) und niedrige spezifische Gateladung (QG x RON = 0,9 nCΩ). Mit einem flächenspezifischen Einschaltwiderstand von RON x A = 0,66 Ωmm2 für die 600-V-Klasse sind die FBH-GaN-Transistoren auch bezüglich der benötigten Chipfläche konkurrenzfähig. Das wesentliche Hindernis zur Markteinführung dieser neuen Leistungshalbleiterbauelemente stellt bislang der hohe Preis der eingesetzten SiC-Substrate dar.

In den letzten Jahren gab es jedoch große Fortschritte beim Wachstum von geeigneten GaN-Schichten mit ausreichender Spannungsfestigkeit auf Silizium-Substraten. Der Preisvorteil beim Einsatz von Si-Substraten bis zu 200 mm Durchmesser wird die Herstellungskosten der GaN-basierten Transistoren so weit reduzieren, dass die 600-V-GaN-Technologie auch bezüglich des Bewertungsfaktors Kosten x (QG x RON) wettbewerbsfähig werden wird.

Im Rahmen des EU FP7 Projekts HipoSwitch hat das FBH seine 600-V-Technologie für selbstsperrende Leistungsschalttransistoren von der GaN-auf-SiC-Plattform auf 4" GaN-auf-Si-Wafer übertragen. DC-Messungen an Testtransistoren mit 3,2 mm Gateweite im Waferverbund zeigen für beide Substrate nahezu gleiche Werte für die Einsatzspannung (Vth = 1,1 V), den Drainstrom unterhalb der Einsatzspannung, den Drainleckstrom im gesperrten Zustand (10 nA/mm für 0 V Gatespannung) und den Gatestrom bei geöffnetem Transistor (4-10 µA/mm bei 5 V Gatespannung).

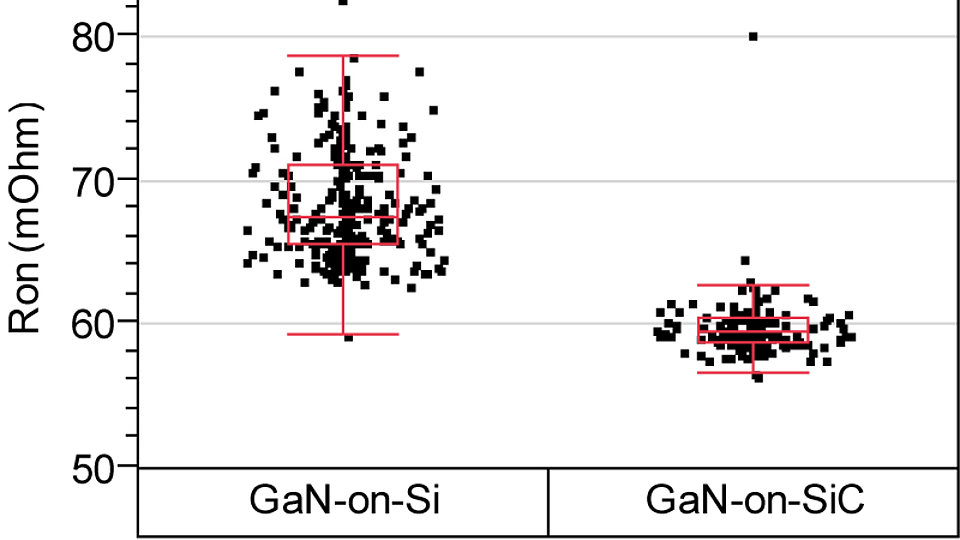

Signifikante Unterschiede zwischen den eingesetzten Substraten zeigen sich aber beim Betrieb mit Verlustleistung. Der maximale Drainstrom der GaN-auf-Si-Transistoren (Idsmax = 0,3 A/mm bei Vds = 7,5 V) liegt bei nur 68% des Stroms der GaN-auf-SiC-Bauelemente. Der geringere Strom kann nur teilweise durch den um 20% höheren Schichtwiderstand des Transistorkanals für den GaN-auf-Si-Wafer erklärt werden. Dieser spiegelt sich nur im unterschiedlichen Einschaltwiderstand der Leistungsschalttransistoren (59 mΩ für GaN-auf-SiC und 67 mΩ für GaN-auf-Si-Transistoren bei 214 mm Gateweite) wider. Die wesentliche Ursache ist vielmehr die erhöhte Kanaltemperatur der GaN-auf-Si-Transistorzellen wenn 7 W und mehr elektrische Leistung auf 0,1 mm2 aktiver Transistorfläche umgesetzt werden müssen. Hier zeigt sich, dass SiC-Substrate mit ihrer im Vergleich zu Silizium dreimal höheren Wärmeleitfähigkeit die Verlustwärme schneller abführen können. Nach dem Abdünnen der Wafer und dem Vereinzeln und Einhäusen der Transistorchips wird sich der Einfluss des Substratmaterials auf die Kanaltemperatur verringern.

Publikationen:

O. Hilt, E. Bahat-Treidel, F. Brunner, A. Knauer, R. Zhytnytska, P. Kotara, J. Wuerfl, "Normally-off GaN Transistors for Power Applications", J. Phys.: Conf. Ser., vol. 494, no. 012001 (2014).

O. Hilt, P. Kotara, F. Brunner, A. Knauer, R. Zhytnytska, J. Würfl, "Improved Vertical Isolation for Normally-off High Voltage GaN-HFETs on n-SiC Substrates", IEEE Transactions on Electron Devices, vol. 60, no. 10, pp. 3084-3090 (2013).

O. Hilt, E. Bahat-Treidel, F. Brunner, A. Knauer, R. Zhytnytska, P. Kotara, J. Wuerfl, "Normally-off GaN Transistors for Power Switching Applications", ECS Trans., vol. 58, no. 4, pp. 145-154 (2013).

FBH-Forschung: 14.08.2014