Erhöhte vertikale Isolation von GaN-basierten Hochspannungstransistoren für die Leistungselektronik

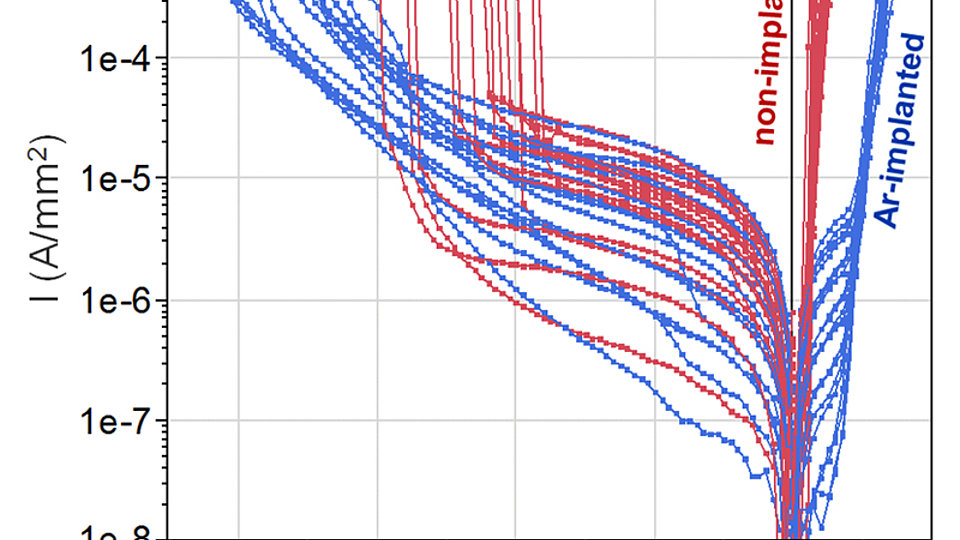

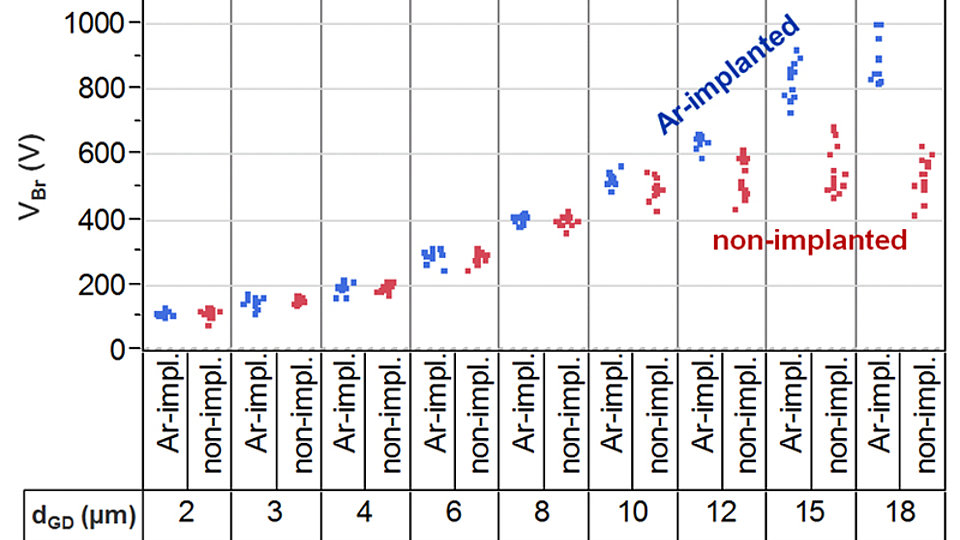

Abb. 1: Vertikale Leckströme an unterschiedlichen Waferpositionen für Wafer mit (blau) und ohne (rot) n-SiC Substratimplantation.

GaN-basierte Hochspannungsschalttransistoren sind die Basis für besonders kompakte und effiziente Leistungskonverter. Sie bieten einen kleinen flächenspezifischen Einschaltwiderstand bezogen auf die Spannungsfestigkeit (RONA/ VBr) und besonders geringe Schaltverluste. Die Durchbruchspannung der AlGaN/GaN-HEMTs erhöht sich mit dem lateralen Gate-Drain-Abstand dGD, typische Werte für die laterale Spannungsfestigkeit liegen bei 50 V/µm. Für Betriebsspannungen von 600 V und mehr werden daher Gate-Drain-Abstände von mehr als 12 µm benötigt.

Im Herstellungsprozess werden die Halbleiterschichten der AlGaN/GaN-HFETs epitaktisch auf Fremdsubstraten abgeschieden, wobei aus Kostengründen leitfähige Substrate wie n-dotiertes SiC oder Si gegenüber semi-isolierendem SiC bevorzugt werden. Die Dicke der abgeschiedenen GaN-Schichten ist wegen der durch die Heteroepitaxie hervorgerufenen Materialverspannungen auf 3 - 5 µm begrenzt. Da über die leitfähigen Substrate keine Spannung abfallen kann, sind die Anforderungen an die vertikale Spannungsfestigkeit der (Al)GaN-Schichten höher als an die laterale Spannungsfestigkeit. Die vertikalen Leckströme wurden an AlGaN/GaN-Heterostrukturen untersucht, die auf einem 3 µm dicken eisendotierten GaN-Puffer beruhen. Tatsächlich limitiert der vertikale Leckstrom die Sperrfähigkeit des Bauelements auf etwa 80 V zwischen Drain und Substrat und auf 400 V zwischen Source und Substrat. Daher ist die Transistorspannungsfestigkeit bei floatendem Substrat auf 500 V begrenzt und steigt ab 10 µm nicht mehr mit zunehmenden Gate-Drain-Abstandan.

Am FBH wurden leitfähige n-SiC-Substrate vor dem epitaktischen Wachstum mit Argon implantiert. Dadurch entsteht eine zusätzliche isolierende Schicht auf der Substratoberseite. Die Transistorstrukturen auf diesen vorimplantierten Substraten weisen reduzierte vertikale Leckströme auf, sodass nun eine vertikale Sperrfähigkeit von 150 V bzw. 700 V erreicht wird. Bei ansonsten identischen Transistoren auf vorimplantierten und nicht implantierten Substraten konnte damit die Transistordurchbruchspannung von 500 V auf 900 V erhöht werden. Die Durchbruchspannung skaliert mit dem Gate-Drain-Abstand auch für größere Abstände als 10 µm.

Viel Aufmerksamkeit wurde der Frage geschenkt, ob die modifizierte Unterlage das Wachstum der GaN-Schichten beeinflusst. Deren Qualität hat sich aber durch die implantierte Substratoberfläche nicht verschlechtert. Ein sorgfältiger Vergleich, sowohl der statischen als auch der dynamischen elektrischen Transistoreigenschaften, zeigt identisches Verhalten auf implantierten und nicht implantierten n-SiC-Substraten. In Röntgenstreuungsanalysen (HRXRD) waren die Halbwertsbreiten der GaN-Reflexionssignale durch die Substratimplantation nicht erhöht, was eine vergleichbare Defektdichte in den GaN-Schichten belegt.

Publikationen:

O. Hilt, P. Kotara, F. Brunner, A. Knauer, R. Zhytnytska, J. Würfl, "Improved Vertical Isolation for Normally-off High Voltage GaN-HFETs on n-SiC Substrates", IEEE Trans. Electron Devices, DOI 10.1109/TED.2013.2259492, 2013.

P. Kotara, R. Zhytnytska, O. Hilt, E. Cho, F. Brunner, A. Thies, J. Würfl, "Vertical blocking voltage improvement of GaN HEMT structures on n-SiC by pre-epitaxial substrate implantation", accepted for publication, ECS Journal of Solid State Science and Technology, Vol. 2(8), pp. N3064-N3067, 2013.

FBH-Forschung: 05.07.2013