Investigation of atomic layer deposition methods of Al2O3 on n-GaN

L. Tadmor1, S.S.T. Vandenbroucke2, E. Bahat Treidel1, E. Brusaterra1, P. Plate3, N. Volkmer1, F. Brunner1, C. Detavernier2, J. Würfl1, and O. Hilt1

Published in:

J. Appl. Phys., vol. 135, vol. 8, pp. 085701, doi:10.1063/5.0189543 (2024).

Abstract:

In this work, three atomic layer deposition (ALD) approaches are used to deposit an Al2O3 gate insulator on n-GaN for application in vertical GaN power switches: thermal ALD (ThALD), plasma-enhanced ALD (PEALD), and their stacked combination. The latter is a novel method to yield the most ideal insulating layer. Also, the influence of an in situ NH3 or H2 plasma pre-treatment is studied. Planar MIS capacitors are used to investigate the electrical properties and robustness of the gate insulators. In vacuo x-ray photoelectron spectroscopy (XPS) is used to study the changes in chemical composition after every surface treatment. XPS shows that all plasma pre-treatments efficiently remove all carbon contamination from the surface, but only NH3 plasma is observed to additionally remove the native oxide from the n-GaN surface. The water precursor step in the ThALD process does not completely remove the CH3 ligands of the trimethylaluminum precursor step, which might electrically be associated with a reduced forward bias robustness. The O2 plasma step in the PEALD process is associated with the removal of carbon and a tremendous increase of the O content in the GaN surface region. Electrically, this strongly correlates to an enhanced forward bias robustness and an increased forward bias hysteresis, respectively. The ThALD/PEALD stack method mitigates the shortcomings of both ALD processes while maintaining its advantages. Electrical measurements indicate that the stack method alongside NH3 plasma pretreatment provides the best characteristics in terms of hysteresis, threshold voltage, forward bias robustness, and interface trap density of states.

1 Ferdinand-Braun-Institut (FBH), Gustav-Kirchhoff-Str. 4, 12489 Berlin, Germany

2 Department of Solid State Sciences, CoCooN Group, Ghent University, Krijgslaan 281/S1, Ghent 9000, Belgium

3 Plasma Process Technology Department, SENTECH Instruments GmbH, 12489 Berlin, Germany

Topics:

Electrical properties and parameters, Field effect transistors, MOS devices, Electric measurements, Dielectric materials, Magnetic hysteresis, Atomic layer deposition, X-ray photoelectron spectroscopy, Oxides, Interfaces

© 2024 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0189543

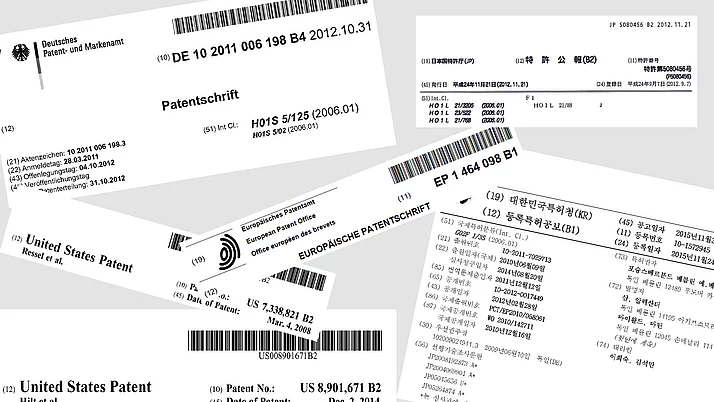

Rightslink® by Copyright Clearance Center

Full version in pdf-format.