Neue in-situ Analysemöglichkeiten für Plasmaätzprozesse am FBH

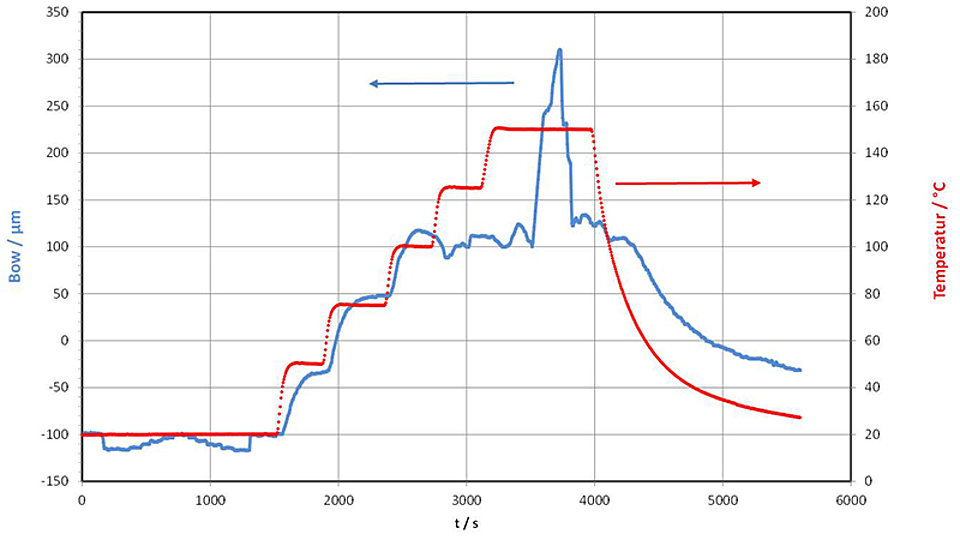

Abb. 2: Verbiegung eines aufgeklebten 100 µm dicken SiC-Wafer auf 1 mm dickem Saphir gemessen mit EpiCurve-System im Plasmareaktor in Abhängigkeit von der Temperatur

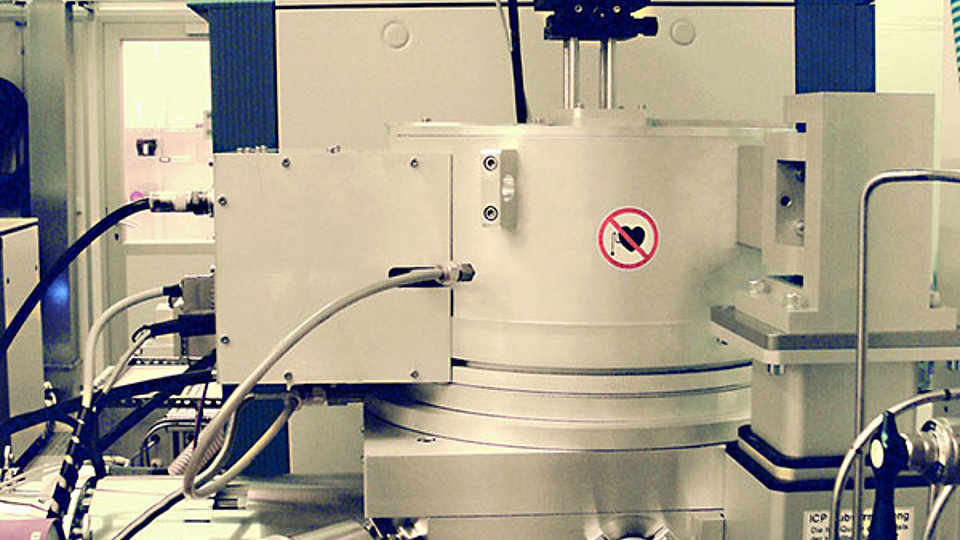

Das trockenchemische Ätzen mittels hochreaktiver Plasmen gehört zu den wichtigsten Strukturierungsverfahren in der Halbleiterprozesstechnologie. Die zu ätzenden Materialien werden dabei z.T. auch thermisch sehr stark beansprucht, was zu thermo-mechanischen Belastungen führt. Dies kann Verformungen zur Folge haben, die die Homogenität des Ätzergebnisses beeinflussen und bis zur mechanischen Zerstörung des Wafers führen. Im Allgemeinen können Verbiegungen der Wafer in einer Plasmaätzkammer nicht direkt verfolgt werden. Dem FBH und der Firma Laytec ist es gelungen, einen kommerziellen Krümmungssensor des Unternehmens so zu modifizieren, dass die Messung von Wafern während des Plasmaätzprozesses möglich ist (Abb. 1). So konnte zum ersten Mal der Einfluss unterschiedlicher Prozessparameter auf die Durchbiegung in einem Plasmaätztool analysiert werden. In Abb. 2 ist beispielhaft der Einfluss der Temperatur auf die Waferverbiegung gezeigt.

Der Sensor wurde erfolgreich zur Optimierung der Prozessbedingungen beim Plasmaätzen von Durchgangslöchern in 100 µm dickes Siliziumcarbid (SiC) angewendet. Materialien dieser Dicke sind biegsam wie Papier und nicht einfach handhabbar. Deshalb werden sie zur Prozessierung vorübergehend auf eine stützende Unterlage geklebt, von der sie nach Abschluss der Prozessierung wieder abgelöst werden müssen. Die Durchführung eines Plasmaätzprozesses auf einem solchen Verbund aus Wafer und Unterlage ist eine besondere Herausforderung. Im Ätzreaktor wird dieser Verbund erwärmt, einerseits durch den Ätzprozess selbst aber auch durch eine Heizung, denn das zu ätzende SiC-Material ist bei erhöhter Temperatur besser ätzbar. Durch Einsatz des Sensors konnten die Ätzparameter so verändert werden, dass die prozessbedingte Verkrümmung des Wafers limitiert wurde, die Ausbeute stieg und die Prozesszeit verkürzt wurde. Die Ergebnisse werden auf der International Conference on Compound Semiconductor Manufacturing Technology (CSMANTECH) im Mai dieses Jahres detailliert vorgestellt.

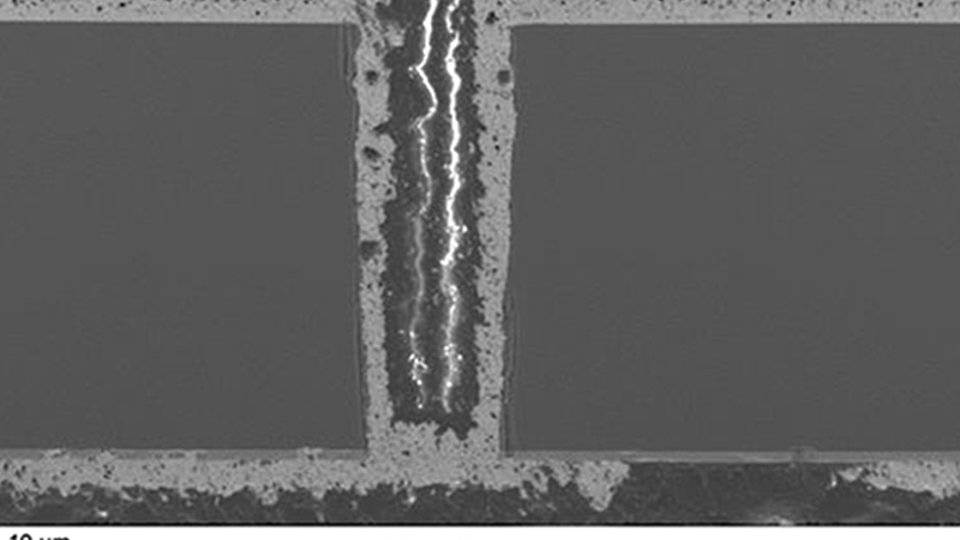

Die Optimierung des Ätzprozesses von SiC zielt auf die Weiterentwicklung der AlGaN/GaN-Transistoren (HEMTs), die auf SiC-Substraten hergestellt werden. Diese Bauelemente modulieren mit ihrem Gate den Strom, der von einem Eingang (Source) zum Ausgang (Drain) fließen soll. Eine vereinfachte Montage der Bauelemente (und eine Reduzierung der Kosten) wird möglich, wenn alle Source-Kontakte durch Vias parallel geschaltet werden. Dabei werden Löcher in den Chip von hinten durch das SiC und AlGaN/GaN bis zum Kontakt auf der Vorderseite geätzt, die dann mit Metall gefüllt werden. So hat man mittels dieser Vias die elektrische Verbindung zwischen der Rückseite und dem Source-Kontakt schon hergestellt, wenn der Chip auf seine Unterlage aufgelötet wird. Das erspart die separate Kontaktierung mit Drähten und eröffnet neue geometrische Möglichkeiten des Aufbaus. Ein Beispiel für einen solchen Via-Kontakt ist in Abb. 3 zu sehen. Damit konnte ein wichtiger Meilenstein für die Weiterentwicklung der Aufbautechnologien von Leistungsverstärkern auf Basis von AlGaN/GaN-Transistoren am FBH erreicht werden.

Publikation:

A. Thies, W. John, S. Freyer, J. Beltran, O. Krüger, "Analysis and Optimization of a Through Substrate Via Etch Process for Silicon Carbide Substrates", CSMANTECH 2015, May 18-21, accepted for publication.

FBH-Forschung: 19.03.2015