# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

H01L

21/285

(2006.01)

H01L

29/20

(2006.01)

H01L

29/45

(2006.01)

H01L

33/00

(2010.01)

H01L

33/36

(2010.01)

H01S

5/042

(2006.01)

H01S

5/22

(2006.01)

H01S

5/323

(2006.01)

(52) CPC특허분류

H01L 21/28575 (2013.01) H01L 29/2003 (2013.01)

(21) 출원번호 10-2016-7015630

(22) 출원일자(국제) **2014년12월17일** 심사청구일자 **2016년07월28일**

(85) 번역문제출일자 2016년06월13일

(65) 공개번호 10-2016-0098241

(43) 공개일자 2016년08월18일

(86) 국제출원번호 PCT/EP2014/078189

(87) 국제공개번호 **WO 2015/091626** 국제공개일자 **2015년06월25일**

(30) 우선권주장

10 2013 226 270.1 2013년12월17일 독일(DE)

(56) 선행기술조사문헌

JP2012094564 A\*

KR1020070092058 A\*

JP02271616 A\*

JP10022274 A

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2018년02월22일

(11) 등록번호 10-1831216

(24) 등록일자 2018년02월14일

(73) 특허권자

포슝스베르분드 베를린 에.베.

독일 베를린 12489 루도버 카우세 17

(72) 발명자

인펠트, 스벤

독일 12621 베를린, 발트스트라세 72 레다엘리, 루카

독일 10997 베를린, 나우니스트라세 10 **크나이슬, 미카엘**

독일 10435 베를린, 우제만스트라세 11

(74) 대리인

특허법인세림

전체 청구항 수 : 총 8 항

심사관 : 강병섭

### (54) 발명의 명칭 반도체 표면 금속 컨택 형성 방법 및 금속 컨택을 가진 장치

#### (57) 12 9

본 발명은 반도체의 표면에 적어도 하나의 금속 컨택을 형성하는 방법 및 적어도 하나의 금속 컨택을 가진 장치에 관한 것이다.

상기 방법은 반도체(10)의 표면(11)에 적어도 하나의 금속 컨택(60)을 형성하기 위해 사용되며, 반도체 표면(11) (뒷면에 계속)

를 표 표 - 도6

위에 금속층(20)을 도포하고, 금속층(20) 위에 마스크(40, 50)를 도포하고, 마스크(40, 50)를 사용하여 적어도 금속층(20)을 구조화하는 단계들을 포함하고, 금속의 측면 증착물(21)이 구조화에 의해 마스크에 생성되어 마스크는 증착물들(21) 및 구조화 이후의 구조화된 금속층(20') 사이에 매립된다. 상기 방법은 전도성 하드 마스크에 의해 특징화된다.

마스크는 전도성이 있기 때문에 금속 내에 매립되어 남을 수 있다. 증착물들을 제거할 필요는 없다. 증착물들과 마스크는 컨택의 일부를 형성한다.

## (52) CPC특허분류

**H01L 29/452** (2013.01)

**H01L 33/0075** (2013.01)

**H01L 33/36** (2013.01)

**H01S 5/0425** (2013.01)

**H01S 5/22** (2013.01)

**H01S 5/32341** (2013.01)

HO1L 2933/0016 (2013.01)

## 명제거

## 경구범위

## 청구항 1

질화갈륨(gallium nitride)으로 만들어진 반도체(10)의 표면(11)에 적어도 하나의 금속 컨택(60)을 형성하기 위한 방법으로서,

상기 반도체(10)의 상기 표면(11) 위에 팔라듐의 금속층(20)을 도포하는 단계와,

상기 금속층(20) 위에 마스크(40, 50)를 도포하는 단계와,

상기 마스크(40, 50)를 사용하여 적어도 상기 금속층(20)을 구조화하는 단계를 포함하고,

상기 금속층의 금속의 측면 중착물(lateral deposits)(21)이 상기 구조화에 의해 상기 마스크에 생성되어 상기 마스크는 상기 중착물들(21) 및 상기 구조화 이후의 상기 구조화된 금속층(20') 사이에 매립되며(embedded),

상기 마스크는 전도성 하드 마스크(conductive hard mask)이고, 상기 구조화는 또한 상기 반도체(10)를 구조화 시키며,

상기 금속층(20)을 아르곤으로 스퍼터 에칭시키는 단계와, 상기 반도체(10)를 염소로 플라즈마 에칭시키는 단계를 더 포함하는 것을 특징으로 하는 방법.

#### 청구항 2

제1항에 있어서,

상기 마스크는 상기 금속과 다른 적어도 하나의 전도성 물질(40)을 구비하며, 상기 적어도 하나의 전도성 물질(40)은 상기 하드 마스크의 최하층을 형성하고, 상기 하드 마스크는 상기 적어도 하나의 전도성 물질(40) 위에 배치되고 상기 금속으로 만들어진 층(50)을 더 구비하는 것을 특징으로 하는 방법.

#### 청구항 3

제2항에 있어서,

상기 전도성 물질(40)은 티타늄, 니켈 또는 크롬을 구비하는 것을 특징으로 하는 방법.

## 청구항 4

제1항 내지 제3항 중의 한 항에 있어서,

상기 반도체(10)는 에피택셜(epitaxial)인 것을 특징으로 하는 방법.

#### 청구항 5

제1항 내지 제3항 중의 한 항에 있어서,

상기 금속 컨택(60)은 릿지 도파로(ridge waveguide)의 일부로 되는 것을 특징으로 하는 방법.

#### 청구항 6

제1항 내지 제3항 중의 한 항에 있어서,

상기 금속 컨택(60)은 마이크로-픽셀 LED 또는 나노-픽셀 LED의 P-측(p-side)에서 메사 구조(mesa structure)로 되는 것을 특징으로 하는 방법.

#### 청구항 7

제1항의 방법에 따라 구조화된 질화갈륨 반도체(10)의 표면(11)에 형성된 적어도 하나의 금속 컨택(60)을 가진 장치로서, 상기 금속 컨택은 대응되게 구조화된 팔라듐 층(20')에, 그리고 팔라듐 증착물들(palladium deposits)(21) 사이에 전도성 하드 마스크 물질을 포함하고,

상기 금속 컨택(60)의 표면 영역은 오목하지 않은 것을 특징으로 하는 장치.

#### 청구항 8

제7항에 있어서,

모든 표면 영역은 편평한 것을 특징으로 하는 장치.

## 발명의 설명

对金融等

[0001] 본 발명은 반도체의 표면에 적어도 하나의 금속 컨택(metal contact)을 형성하는 방법 및 적어도 하나의 금속 컨택을 가진 장치에 관한 것이다.

#### 明得对对象

- [0002] 예를 들어 질화 갈륨(GaN; gallium nitride)과 같은 반도체는 다양한 기술분야에서 사용된다. 일 실예로는 레이저 다이오드를 위한 릿지 도파로(ridge waveguides)를 제조하기 위한 에피택셜 반도체 웨이퍼(epitaxial semiconductor wafers)의 사용이다.

- [0003] 이러한 많은 응용은 반도체의 표면에 금속 컨택(metal contacts)을 요구한다. 여기서, 그와 같은 금속 컨택의 저항값은 각각의 금속 컨택의 적용 시 불순물 및/또는 결정 결함(crystal defects) 및/또는 반도체 표면의 화학 량론(the stoichiometry of the semiconductor surface)에 민감하게 좌우된다. 반도체 표면의 화학량론은 특히 반도체의 처리 중에 변할 수 있다.

- [0004] 금속 접촉의 저항값이 그것으로부터 영향을 받지 않게 하기 위해, 각각의 금속층은 각 다른 반도체의 처리과정 전에 반도체 표면에 증착되고 마스크에 의해 공제적으로(subtractively) 구조화된다. 금속 컨택(metal contacts)이 값비싸고 화학적으로 매우 불활성의 금속으로 이루어지는 경우, 이러한 목적을 위해 건식 에칭 방법, 예를 들어 스퍼터 에칭(sputter etching), 반응성 이온 에칭(RIE: reactive-ion etching), 유도 결합 플라즈마(ICP: inductively coupled plasma) 에칭, 또는 화학적 보조 이온빔 에칭(chemically assisted ion beam etching)이 요구된다.

- [0005] 그와 같은 건식 에칭 방법에 있어서, 제거된 금속의 일부는 재증착 과정에서 마스크의 표면과 엣지 뿐만 아니라 다시 그 표면에 증착된다. 마스크 제거 후, 마스크의 엣지에 증착되었던 금속은 일종의 펜스(fence)로서 남게 된다. 이 펜스는 제거하기가 어려우며, 열수송(heat transport)을 방해함으로써 반도체를 포함한 그 컴포넌트 (component)의 신뢰성에 영향을 줄 수 있는, 증착 과정에서 캐비티의 형성을 야기할 수 있다.

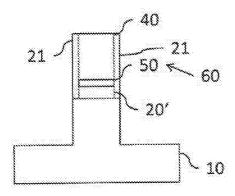

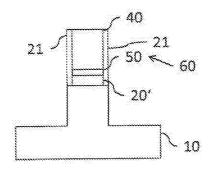

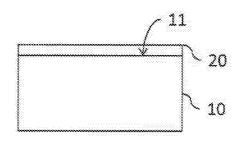

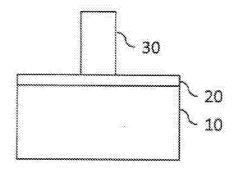

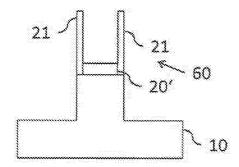

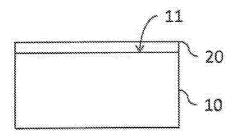

- [0006] 종래기술에 따른 펜스의 형성은 도 1 내지 도 3에 예시되어 있다. 도 1은 반도체(10)의 표면(11)에 팔라듐(Pb: palladium)의 금속층(20)을 가진 질화갈륨(GaN)의 구조화되지 않은(unstructured) 반도체(10)를 나타낸 것이다. 도 2에 도시된 바와 같이, 마스크(30), 예컨대 SiNx의 하드 마스크(hard mask)가 도포된다(applied). 이때, 금속층(20)은 스퍼터 에칭에 의해 예를 들어 아르곤으로 구조화된다. 그후, 반도체(10)는 동일한 마스크를 사용하여 플라즈마 에칭에 의해 예를 들어 염소(chlorine)로 구조화된다. 그리고 나서, 마스크의 잔류물이 제거된다. 도 3에 도시된 바와 같이, 마스크의 제거 후 마스크에서 측면에 중착되어 구조화된 금속층(20') 위에서 상향으로 돌출한 중착물(deposits)(21)을 가진 구조체가 남는다.

- [0007] 마스크의 제거는 예를 들어, 불화수소산(hydrofluoric acid)을 사용하여 습식 화학적으로(wet-chemically) 수행된다.

- [0008] 티타늄 마스크에 의해 구조화된 텅스텐 층을 형성하기 위한 방법이 문헌 US 5,176,792에 기술되어 있다. 문헌 EP 0 889 519 A2는 캐패시터를 위한 전극 구조와 관련된다. 플라티늄 전극이 Ti-Al-N 하드 마스크(hard mask)에 의해 에칭되며, 에칭 중에 플라티늄의 재증착(redeposition)은 일시적인 측벽 펜스들의 형성을 이끈다. 문헌 US 6,433,436 B1은 일 단계에서의 조합된 에칭 공정에서 멀티 레벨 상호연결 구조(multi-level-interconnected structure)의 제조를 예시한다. 문헌 DE 10 2009 034 359 A1은 발광 다이오드, 특히 질화갈륨(GaN)에 기반하는

나노 픽셀 엘이디(nano-pixel LED)를 위한 팔라듐 기반의 p-컨택(palladium-based p-contact)에 관한 것이다.

발명의 내용

#### 해결하려는 과제

[0009] 본 발명의 목적은 신뢰성 있게 기능하는 금속 컨택이 반도체의 표면에 형성될 수 있는 방법을 제공하는 것이다.

## 과제의 해결 수단

- [0010] 이러한 목적은 청구항 제1항에 따른 방법에 의해 실현된다. 상기 방법은 질화갈륨(gallium nitride)으로 만들어 진 반도체의 표면에 적어도 하나의 금속 컨택을 형성하기 위해 사용되며, 반도체 표면 위에 팔라듐의 금속층을 도포하는(applying) 단계와, 상기 금속층 위에 마스크를 도포하는 단계와, 상기 마스크를 사용하여 적어도 상기 금속층을 구조화하는 단계를 포함하고, 상기 금속층의 금속의 측면 증착물(lateral deposits)(21)이 상기 구조화에 의해 상기 마스크에 생성되어 상기 마스크는 상기 증착물들(deposits) 및 상기 구조화 이후의 상기 구조화된 금속층 사이에 매립된다(embedded). 상기 방법은 상기 마스크는 전도성 하드 마스크(conductive hard mask)이고, 상기 구조화는 또한 상기 반도체를 구조화시키고, 상기 금속층을 아르곤으로 스퍼터 예칭시키는 단계와, 상기 반도체를 염소로 플라즈마 에칭시키는 단계를 포함하는 것을 특징으로 한다.

- [0011] 상기 마스크는 전도성이 있기 때문에 분실 마스크(lost mast)의 역할을 할 수 있으며, 상기 금속 컨택의 어떤 표면 부분도 오목하지 않도록 상기 마스크와 상기 측면 증착물을 제거할 필요가 없다. 상기 증착물 및 상기 손실 마스크는 상기 컨택의 일부를 형성한다.

- [0012] 유리한 실시예에 있어서, 상기 마스크는 상기 금속과 다른 적어도 하나의 전도성 물질을 구비한다. 이러한 경우, 상기 다른 물질은 상기 하드 마스크의 최하층을 형성할 수 있다. 또한, 상기 유리한 실시예의 상기 하드 마스크는 상기 다른 물질 위에 배치되고 상기 금속으로 만들어진 층을 구비한다.

- [0013] 상기 구조화의 결과로서, 상기 금속은 상기 다른 물질을 에워싸서 상기 컨택의 전도성이 상기 컨택 내의 상기 물질의 존재에 의해 최소한으로만 영향을 받도록 한다.

- [0014] 상기 전도성 물질은 예를 들어, 티타늄, 니켈 또는 크롬을 구비할 수 있다.

- [0015] 상기 반도체는 에피택셜 반도체로 될 수 있다. 상기 금속 컨택은 릿지 도파로(ridge waveguide)의 일부로 될 수 있다. 상기 금속 컨택은 또한 마이크로-픽셀 LED 또는 나노-픽셀 LED의 P-측(p-side)에서 메사 구조(mesa structure)로 될 수 있다.

- [0016] 본 발명에 따르면, 구조화된 질화갈륨 반도체의 표면에 적어도 하나의 금속 컨택을 가진 청구항 제7항에 따른 장치가 더 제시된다. 상기 장치는 상기 금속 컨택은 대응되게 구조화된 팔라듐 층에, 그리고 팔라듐 증착물들 (palladium deposts) 사이에 전도성 하드 마스크 물질을 포함하고, 상기 금속 컨택의 모든 표면 영역은 볼록하 거나 편평한 것을 특징으로 한다. 즉, 상기 금속 컨택의 어떠한 표면 영역도 오목하지 않다.

## 도면의 간단한 설명

[0017] 본 발명의 실시예가 관련 도면을 참조하여 아래에 기술된다.

도 1 내지 도 3은 종래기술에 따른 금속 컨택을 형성하기 위한 방법 중 반도체의 여러 상태를 개략적으로 나타 낸 것이다.

도 4 내지 도 6은 본 발명의 일 실시예에 따른 금속 컨택을 형성하기 위한 방법 중 반도체의 여러 상태를 개략 적으로 나타낸 것이다.

## 발명을 실시하기 위한 구체적인 내용

- [0018] 도 4는 반도체(10)의 표면(11)에 팔라듐(palladium: Pd)의 금속층(20)을 가진 질화갈륨(GaN)의 구조화되지 않은 반도체(10)를 나타낸 것이다. 이 실예의 구조화되지 않은 반도체(10)는 에피택셜 반도체이지만, 본 발명은 또한 다른 반도체들을 위해 그 기술적 효과를 발전시키며, 에피텍셜 반도체로 제한되지 않는다.

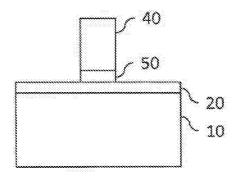

- [0019] 도 5에 나타낸 바와 같이, 티타늄(titanium: Ti)의 최하층(50)을 구비하는 전도성 하드 마스크(40, 50)가 도포 된다. 팔라듐 이외의 다른 전도성 물질은 니켈(Nickel: Ni)과 크롬(chromium: Cr)이다. 최하층(50) 위에 배치되

는 최상층(40)도 또한 팔라듐으로 이루어진다. 최상층(40)은 선택적이며, 이 실예에서는 금속층(20)보다 상당히 두껍다. 이 실예에서는 최상층(40)이 최하층(50) 위에 직접 배치되도록 오직 두 개의 층이 제시되어 있다. 그러나, 본 발명의 의미(sense)에서 추가적인 전도성 층들도 가능하다. 오직 하나의 층만이 사용된다면, 다른 전도성 물질의 전기적 특성이 상기 금속의 것과 더 유사한 것이 더 유리하다. 특히, 상기 하드 마스크는 또한 금속층(20)의 금속으로 이루어질 수 있다.

[0020] 그 다음으로, 금속층(20)은 예컨대 아르곤으로 스퍼터 에칭에 의해 구조화되는 바, 즉 비 마스킹 영역(non-masked area)에서 제거된다. 여기서, 최상층(40)은 대응되게 제거되지만, 그것은 금속층(20)보다 더 두껍기 때문에, 금속층(20)이 비 마스킹 영역에서 이미 완전히 제거되면 최상층(40)으로부터의 잔류물이 남는다.

[0021] 비 마스킹 영역에서, 그리고 최상층(40)의 표면으로부터 제거된 금속은 금속의 증착물(deposits)(21)의 형태로 구조화된 금속층(20') 및 마스크의 층들(40, 50)에서 측면에 증착하다.

이후, 반도체(10)는 동일한 마스크를 사용하여 예컨대 염소로 플라즈마 에칭에 의해 구조화된다.

도 6에 나타낸 바와 같이, 증착물(deposits)(21) 및 충들(20', 50)은 충(40)의 다른 전도성 물질을 에워싼다. 하드 마스크의 잔류물, 즉 충(50)과 충(40)의 잔류물은 모두 전도성이고 컨택(contacts)의 일부로서 사용될 수 있어서 마스크와 증착물(deposits)은 제거되지 않아야 한다. 따라서, 금속 컨택의 오목한 표면 영역이 생성되지 않는다. 부가해서, 본 발명에 따라 제시된 방법은 보다 적은 방법 단계를 요구한다. 상기 컨택은 충(40)의 잔류물의 표면을 통해 용이하게 접촉될 수 있으며, 중착물(deposits)(21) 사이의 캐비티(cavity)는 채워져서 중착물(21)을 제거할 필요가 없다. 따라서, 본 발명에 따라 제시된 장치는 더 신뢰성 있고 더 기능성이 있다.

[0024] 본 발명의 의미에서 금속 컨택(metal contacts)은 다양한 응용을 위해 유리하게 사용될 수 있다. 예를 들어, 상기 금속 컨택은 릿지 도파로의 일부가 될 수 있다. 예를 들어, 상기 금속 컨택은 마이크로-픽셀 LED 또는 나노-픽셀 LED의 p-측(p-side)에서 메사 구조(mesa structure)로 되는 것도 또한 가능하다.

일 실시예에 있어서, 금속 컨택은 대응되게 구조화된 팔라듐 층 위에, 그리고 팔라듐 증착물들(palladium deposits) 사이에 전도성 하드 마스크 물질을 포함하며, 상기 금속 컨택의 모든 표면 영역은 볼록하거나 편평하다. 즉, 본 실시예에 있어서, 금속 컨택의 어떠한 표면 영역도 오목하지 않다.

是例

[0022]

[0023]

[0025]

X 61

延迟2

##3

*도면4*

X:85

*压图6*